# Industrial IoT Baremetal Framework Developer Guide

# Contents

| Chapter 1 Introduction                       | . 3 |

|----------------------------------------------|-----|

| 1.1 QorlQ layerscape processor               |     |

| 1.2 Baremetal framework for QorlQ layerscape |     |

| 1.3 Supported processors and boards          | 4   |

| Chapter 2 Getting started                                 | 5  |

|-----------------------------------------------------------|----|

| 2.1 Hardware and software requirements                    |    |

| 2.2 Hardware setup                                        |    |

| 2.2.1 LS1021A-IoT board                                   | 5  |

| 2.2.2 LS1028ARDB, LS1043ARDB, or LS1046ARDB               | 6  |

| 2.3 Building the baremetal images from U-Boot source code |    |

| 2.3.1 Building U-Boot binary for the master core          | 7  |

| 2.3.2 Building baremetal binary for slave cores           |    |

| 2.4 Building the image through OpenIL                     |    |

| 2.4.1 Getting OpenIL                                      |    |

| 2.4.2 Building the baremetal images                       |    |

| 2.4.3 Booting up the Linux with Baremetal                 | 11 |

| Chapter 3 Running examp | oles1 | 12 |

|-------------------------|-------|----|

|                         |       |    |

|                         |       |    |

### Chapter 4 Development based on baremetal framework......14

| 4.1 Developing the baremetal application |  |

|------------------------------------------|--|

| 4.2 Example software                     |  |

| 4.2.1 Main file app.c                    |  |

| 4.2.2 Common header files                |  |

| 4.2.3 GPIO file                          |  |

| 4.2.4 I2C file                           |  |

| 4.2.5 IRQ file                           |  |

| 4.2.6 QSPI file                          |  |

| 4.2.7 Ethernet                           |  |

| 4.2.8 USB file                           |  |

| 4.2.9 PCIe file                          |  |

| 4.2.10 CAN file                          |  |

| 4.2.11 ENETC file                        |  |

| 4.3 ICC module                           |  |

| 4.3.1 ICC examples                       |  |

| 4.4 Hardware resource allocation         |  |

| 4.4.1 LS1021A-IoT board                  |  |

| 4.4.2 LS1043ARDB or LS1046ARDB board     |  |

| 4.4.3 LS1028ARDB board                   |  |

| <b>Chapter 5 Revision histo</b> | y35 |

|---------------------------------|-----|

|---------------------------------|-----|

# Chapter 1 Introduction

This document provides an overview of the OpenIL Baremetal framework, the features it supports, and getting started with baremetal framework using the supported NXP Layerscape platforms. It also describes how to run a sample baremetal framework on the host environment and develop customer specific applications based on QorIQ Layerscape baremetal framework.

### 1.1 QorlQ layerscape processor

QorIQ layerscape processors are based on Arm<sup>®</sup> technology.

With the addition of NXP's next-generation QorIQ Layerscape series processors built on Arm core technology, the processor portfolio extends performance to the smallest form factor—from power-constrained networking and industrial applications to new virtualized networks and embedded systems requiring an advanced datapath and network peripheral interfaces.

### 1.2 Baremetal framework for QorlQ layerscape

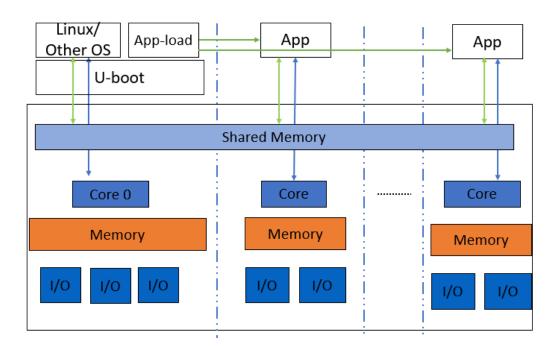

The baremetal framework targets to support the scenarios that need low latency, real-time response, and high-performance. There is no OS running on the cores and customer specific application runs on that directly. The figure below depicts the baremetal framework architecture.

#### Figure 1. Baremetal framework architecture

The main features of the baremetal framework are as follows:

- · Core0 runs as master which runs the operating system such as Linux, Vxworks.

- Slave cores run on the baremetal application.

- Easy assignment of different IP blocks to different cores.

Introduction

- Interrupts between different cores and high-performance mechanism for data transfer.

- Different UART for core0 and slave cores for easy debug.

- Communication via shared memory.

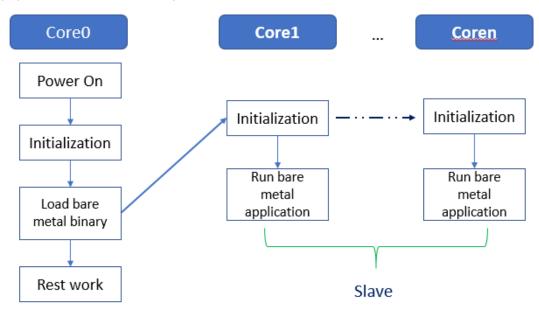

The master core0 runs the U-Boot, it then loads the baremetal application to the slave cores and starts the baremetal application. The following figure depicts the boot flow diagram:

Figure 2. Baremetal framework boot flow diagram

### 1.3 Supported processors and boards

The table below lists the industrial IoT features supported by various NXP processors and boards.

| Processor | Board       | Main features supported                                                              |

|-----------|-------------|--------------------------------------------------------------------------------------|

| LS1021A   | LS1021A-IoT | GPIO, IRQ, IPI, data transfer, IFC, I2C, UART, QSPI, USB, PCIE, Flexcan              |

| LS1043A   | LS1043ARDB  | GPIO, IRQ, GPIO, IPI, data transfer, Ethernet, IFC, I2C, UART, FMan, USB, PCIe       |

| LS1046A   | LS1046ARDB  | GPIO, IRQ, GPIO, IPI, data transfer, Ethernet, IFC, I2C, UART, FMan, QSPI, USB, PCIe |

| LS1028A   | LS1028ARDB  | 12C                                                                                  |

# Chapter 2 Getting started

This section describes how to set up the environment and run the baremetal examples on slave cores (assuming that the core0 is the master core and the other cores are the slave cores).

### 2.1 Hardware and software requirements

The following are required for running baremetal framework scenarios:

- Hardware: LS1021A-IoT, LS1043ARDB, LS1046ARDB, LS1028ARDB, or other QorIQ Layerscape boards and serial cables

- Software: OpenIL v1.4 release or later

### 2.2 Hardware setup

This section describes the hardware setup required for the NXP boards for running the baremetal framework examples.

### 2.2.1 LS1021A-IoT board

Two serial cables are needed. One is used for core0, which connects to USB0/K22 port for UART0, and another one is used for slave cores, which connect J8 and J17 together for UART1. The table below describes the pins for UART1.

| Pin name | Function   |

|----------|------------|

| J8 pin7  | Ground     |

| J17 pin1 | Uart1_SIN  |

| J17 pin2 | Uart1_SOUT |

#### Table 2. UART pins

The figure below depicts the UART1 hardware connections.

Figure 3. UART1 hardware connection

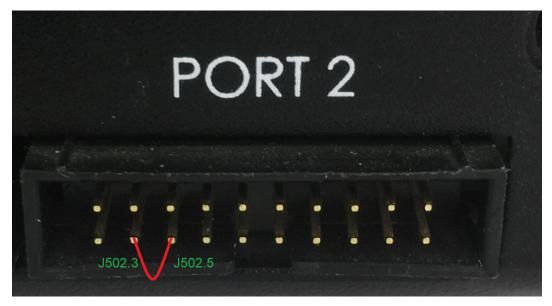

In order to test GPIO, connect the two pins, GPIO24 and GPIO25 together, which are through J502.3 and J502.5.

Figure 4. GPIO24 and GPIO25 connection on LS1021A-IoT

### 2.2.2 LS1028ARDB, LS1043ARDB, or LS1046ARDB

In case, either the LS1028ARDB, LS1043ARDB, or LS1046ARDB is used for developing the OpenIL Baremetal framework, two serial cables are needed. One is used for core0, which connects to UART1 port, and the other one is used for slave cores, which connects to the UART2 port.

#### 2.3 Building the baremetal images from U-Boot source code

There are two methods to build the baremetal images. One method is to compile the images in a standalone way, which is described in this section. Another method is to build the bare metal images using OpenIL framework, which is described in Building the image through OpenIL on page 8.

### 2.3.1 Building U-Boot binary for the master core

Perform the steps mentioned below:

1. Download U-Boot source from the path below:

https://github.com/openil/u-boot.git.

- 2. Check it out to the tag OpenIL-u-boot-201904.

- 3. Configure cross-toolchain on your host environment.

- 4. Then, build the U-Boot and flash it into the SD card as SD boot for core0 using the commands below:

```

/* building u-boot image for ls1021aiot board */

$make ls1021aiot_sdcard_baremetal_defconfig

$make

```

#### NOTE

The default setting enables CAN3/4 feature for baremetal. If you want to enable the GPIO baremetal feature, you need to run the following commands:

```

$make ls1021aiot_sdcard_baremetal_defconfig

$make menuconfig

ARM architecture --->

Baremetal feature select (GPI03_15/27 supported) --->

$make

```

For the LS1028ARDB, LS1043ARDB, or LS1046ARDB, use the following commands:

- /\* building u-boot image for ls1028ardb board \*/

\$make ls1028ardb\_sdcard\_baremetal\_defconfig

\$make

- /\* building u-boot image for ls1043ardb board \*/

\$make ls1043ardb\_sdcard\_baremetal\_defconfig

\$make

- /\* building u-boot image for ls1046ardb board \*/

\$make ls1046ardb\_sdcard\_baremetal\_defconfig

\$make

#### 2.3.2 Building baremetal binary for slave cores

Perform the steps mentioned below:

1. Download the project source from the following path:

https://github.com/openil/u-boot.git.

#### Getting started

- 2. Check it out to the tag OpenIL-Baremetal-201904.

- 3. Configure cross-toolchain on your host environment.

- 4. Then run the following commands:

```

$git checkout baremetal

/* build baremetal image for ls1021-iot board */

$make ls1021aiot_baremetal_defconfig

$make

/* build baremetal image for ls1028ardb board */

$make ls1028ardb_sdcard_baremetal_defconfig

$make

/* build baremetal image for ls1043ardb board */

$make ls1043ardb_defconfig

$make

/* build baremetal image for ls1046ardb board * /

$make ls1046ardb_baremetal_defconfig

$make

```

5. Finally, the file, U-Boot.bin used for bare metal is generated. Copy it to the the the server directory.

### 2.4 Building the image through OpenIL

There are two methods to build the baremetal images. One method is to compile the images in a standalone way which is described in Building the baremetal images from U-Boot source code on page 7. The second method is to build the bare metal images using OpenIL framework, which is described in this section.

The OpenIL project (Open Industry Linux) is designed for embedded industrial usage. It is an integrated Linux distribution for industry. With the OpenIL v1.1 or later releases, the Baremetal can be built and implemented conveniently.

Currently, there are two LS1021A-IoT baremetal defconfig files, a LS1028ARDB baremetal defconfig file, a LS1043ardb baremetal defconfig file;

- configs/nxp\_ls1021aiot\_baremetal\_defconfig

- configs/nxp\_ls1021aiot\_baremetal\_ubuntu\_defconfig

- configs/nxp\_ls1028ardb\_baremetal-64b\_defconfig

- configs/nxp ls1043ardb baremetal-64b defconfig

- configs/nxp\_ls1046ardb\_baremetal-64b\_defconfig

### 2.4.1 Getting OpenIL

OpenIL v1.5 release is available at the following URL:

https://github.com/openil/openil.git.

To follow development, make a clone of the Git repository using the command below:

```

$ git clone https://github.com/openil/openil.git

$ cd openil

# checkout to the tag OpenIL-201904

```

```

$ git checkout -b OpenIL-201904 OpenIL-201904

```

- NOTE

- Build everything as a normal user. Root user permissions are not required for configuring and using OpenIL. By running all commands as a regular user, you protect your system against packages behaving badly during compile and installation.

- Do not use make -jN to build OpenIL as the top-level parallel make is currently not supported.

#### CAUTION

The parameter PERL\_MM\_OPT would be defined in case Perl local::lib is installed on your system. You should unset this option before starting Buildroot, otherwise the compilation of Perl related packages will fail. For example, you might encounter the error information of the PERL\_MM\_OPT parameter while running the make command in a host Linux environment such as this:

```

make[1]: *** [core-dependencies] Error 1

make: *** [_all] Error 2

```

To resolve it, just unset the PERL\_MM\_OPT option.

\$ unset PERL\_MM\_OPT

#### 2.4.2 Building the baremetal images

This section describes the steps for building the baremetal images for LS1021A-IoT, LS1043ARDB, and LS1046ARDB boards.

#### 2.4.2.1 Building the baremetal images for LS1021-IoT board

The two LS1021A-IoT Baremetal default configuration files can be found in the configs directory.

```

• configs/nxp_ls1021aiot_baremetal_defconfig

```

```

• configs/nxp_ls1021aiot_baremetal_ubuntu_defconfig

```

The files include all the necessary U-Boot, Baremetal, kernel configurations, and application packages for the filesystem. Based on these files, you can build a complete Linux + Baremetal environment for the LS1021A-IoT platform without any major changes.

To build the final LS1021A-IoT Baremetal images, run the following commands:

```

$ cd openil

$ make nxp_ls1021aiot_baremetal_defconfig

$ make

# or make with a log

$ make 2>&1 | tee build.log

```

NOTE

The make clean command should be implemented before any other new compilation.

After the correct compilation, you can find all the images for the platform in the output/images directory.

Here is a view of the directory, output/images/:

bm-u-boot.bin --- baremetal image run on slave core

- ---- boot.vfat

- Is1021a-iot.dtb --- dtb file for Is1021a-iot

- ---- rootfs.ext2

- rootfs.ext2.gz

- --- rootfs.ext2.gz.uboot --- ramdisk can be used for debug on master core

#### Getting started

rootfs.ext4.gz -> rootfs.ext2.gz

---- rootfs.tar

sdcard.img --- entire image can be programmed into the SD

uboot-env.bin

u-boot-with-spl-pbl.bin --- uboot image for ls1021a-iot master core

ulmage --- kernel image for Is1021a-iot master core

L-version.json

For more details about Open Industry Linux, refer to the document Open\_Industrial\_Linux\_User\_Guide.

# 2.4.2.2 Building the baremetal images for LS1028ARDB, LS1043ARDB, or LS1046ARDB

The baremetal default configuration files for LS1028ARDB, LS1043ARDB, or LS1046ARDB are located in the *configs* directory. These are:

- configs/nxp\_ls1028ardb\_baremetal-64b\_defconfig

- configs/nxp\_ls1043ardb\_baremetal-64b\_defconfig

- configs/nxp\_ls1046ardb\_baremetal-64b\_defconfig

These files include all the necessary U-Boot, Baremetal, kernel configurations, and application packages for the filesystem. Based on these files, you can build a complete Linux + Baremetal environment for the LS1043A-RDB or LS1046A-RDB platform without any major changes.

Run the following commands to build the final LS1043ARDB or LS1043ARDB baremetal images:

\$ cd openil

Then:

```

$ make nxp_ls1028ardb_baremetal-64b_defconfig

```

or

```

$ make nxp_ls1043ardb_baremetal-64b_defconfig

```

or

```

$ make nxp_ls1043ardb_baremetal-64b_defconfig

```

Then, use:

```

$ make

# or make with a log

$ make 2>&1 | tee build.log

```

NOTE

The  ${\tt make \ clean}$  command should be implemented before any other new compilation.

After the correct compilation, you can find all the images for the platform in the output/images directory.

Here is a view of the directory, *output/images/* for ls1043a-rdb:

---- bm-u-boot.bin --- baremetal image run on slave core

- boot.vfat

```

fsl-ls1043a-rdb-sdk.dtb --- dtb file for ls1043a-rdb

rootfs.ext2

rootfs.ext2.gz

rootfs.ext2.gz.uboot --- ramdisk can be used for debug on master core

rootfs.ext4.gz -> rootfs.ext2.gz

rootfs.tar

sdcard.img --- entire image can be programmed into the SD

uboot-env.bin

u-boot-with-spl-pbl.bin --- uboot image for ls1043ardb master core

kernel-ls1043a-rdb.itb --- kernel, dtb, and rootfs image for ls1043ardb master core

```

L-version.json

For more details about Open Industry Linux, refer to the document Open\_Industrial\_Linux\_User\_Guide.

### 2.4.3 Booting up the Linux with Baremetal

Use the following steps to bootup the Linux + Baremetal system with the images built from OpenIL.

For platforms that can be booted up from the SD card, there is just one step required to program the sdcard.img into SD card.

- 1. Insert an SD card (of at least 2 GB size) into any Linux host machine.

- 2. Then, run the following commands:

\$ sudo dd if=./output/images/sdcard.img of=/dev/sdx

- # or in some other host machine:

- \$ sudo dd if=./output/images/sdcard.img of=/dev/mmcblkx

- # find the right SD Card device name in your host machine and replace the "sdx" or "mmcblkx".

- 3. Then, insert the SD card into the target board (LS1021A-IoT) and power on.

After the above mentioned steps are complete, the Linux system is booted up on the master core (core 0), and the Baremetal system is booted up on slave core (core 1) automatically.

# Chapter 3 Running examples

The following sections describe how to run the baremetal examples on the host environment for LS1021A-IoT board. Similar steps can be followed for LS1028A, LS1043A, and LS1046A reference design boards (RDB).

### 3.1 Preparing the console

Prepare a USB to TTL serial line, connect the pins to LPUART of Arduino pins to use it as UART1, please refer to Hardware setup on page 5.

In order to change LPUART to UART pins, modify 44<sup>th</sup> byte of RCW to 0x00.

In current baremetal framework design, two UART ports are used as console. UART1 is used for master core and UART2 is used for slave cores.

- For LS1021A, UART2 is pin-muxed with LPUART, so need to change the RCW to enable UART2 on master core. This

modification has been implemented in the code for LS1021A-IoT board, so no need to do any code modification for this board.

- For customer specific boards, you need to apply the change to the RCW file:

```

bit[354~356] = 000

bit[366~368] = 111

```

### 3.2 Running the bare metal binary

As described earlier, there are two methods to compile the baremetal framework, a standalone method and using OpenIL. These are described in Building the baremetal images from U-Boot source code on page 7 and Building the image through OpenIL on page 8 respectively. If using OpenIL to compile the baremetal image, the barematal image is included in the sdcard.img and the master core runs the baremetal image on slave cores automatically. If using the standalone compilation method, you need to perform the steps below to run the baremetal binary from U-Boot prompt of master core:

1. After starting U-Boot on the master, download the bare metal image: u-boot.bin on 0x84000000 using the command below:

=> tftp 0x84000000 xxxx/u-boot.bin

Where

- xxxx is your tftp server directory.

- 0x84000000 is the address of CONFIG\_SYS\_TEXT\_BASE on bare metal.

- 2. Then, start the baremetal cores using the command below:

=> cpu start 0x84000000

3. Last, the UART1 port displays the logs, and the bare metal application runs on slave cores successfully.

The figure below displays a sample output log.

```

U-Boot 2017.07-21736-g7fb4afc-dirty (Mar 15 2018 - 15:50:12 +0800)

CPU:

Freescale LayerScape LS1021E, Version: 2.0, (0x87081120)

Clock Configuration:

CPU0(ARMV7):1000 MHz,

Bus:300 MHz, DDR:800 MHz (1600 MT/s data rate),

Reset Configuration Word (RCW):

00000000: 0608000a 0000000 00000000 00000000

00000010: 20000000 08407900 60025a00 21046000

00000020: 0000000 0000000 0000000 00038000

00000030: 20024800 841b1340 00000000 00000000

I2C:

ready

I2C: ready

DRAM: 256 MiB

EEPROM: NXID v16777216

In:

serial

Out: serial

Err: serial

Core[1] in the loop...

i2c read: 0xa0

[ok]i2c test ok

IRQ 0 has been registered as SGI

IRQ 195 has been registered as HW IRQ

SGI signal: Core[l] ack irq : 0

[ok]GPIO test ok

```

Figure 5. Baremetal output logs

# Chapter 4 Development based on baremetal framework

This chapter describes how to develop customer specific application based on QorIQ layerscape baremetal framework.

## 4.1 Developing the baremetal application

The directory "app" in the U-boot repository includes the test cases for testing the I2C, GPIO and IRQ init features. You can write actual applications and store them in this directory.

## 4.2 Example software

This section describes how to analyze a GPIO sample code and use it to write the actual application.

### 4.2.1 Main file app.c

The file <industry-Uboot path>/app/app.c, is the main entrance for all applications. Users can modify the app.c file to add their applications.

- If using standalone method to build the baremetal image as described in Building the baremetal images from U-Boot source code on page 7, just change the directory to industry-Uboot path to check the app.c file.

- If using OpenIL to compile the baremetal binary, you need to change the directory to output/build/bm-uboot-Baremetal-Framework/ to check the app.c file.

The following is a sample code of the file app.c that shows how to add the example test cases of I2C, IRQ, and GPIO.

```

void corel_main(void)

{

test_i2c();

test_irq_init();

test_gpio();

return;

}

```

### 4.2.2 Common header files

There are some common APIs provided by baremetal. The table below describes the header files that include the APIs.

| Header file    | Description                                                                     |

|----------------|---------------------------------------------------------------------------------|

| asm/io.h       | Read/Write IO APIs.<br>For example,raw_readb,raw_writeb, out_be32, and in_be32. |

| linux/string.h | APIs for manipulating strings.<br>For example, strlen, strcpy, and strcmp.      |

Table continues on the next page...

| Header file   | Description                                                    |

|---------------|----------------------------------------------------------------|

| linux/delay.h | APIs used for small pauses.<br>For example, udelay and mdelay. |

| linux/types.h | APIs specifying common types.<br>For example,u32 andu64.       |

| common.h      | Common APIs.<br>For example, printf and puts.                  |

Table 3. Common header file description (continued)

#### 4.2.3 GPIO file

The file uboot/app/test\_gpio.c is one example to test the GPIO feature, and shows how to write a GPIO application.

Here is an example for the Is1021aiot board:

On Is1021aiot board, first you need the GPIO header file, asm-generic/gpio.h, which includes all interfaces for the GPIO. Then, configure GPIO25 to OUT direction, and configure GPIO24 to IN direction. Last, by writing the value 1 or 0 to GPIO25, you can receive the same value from GPIO24.

The table below shows the APIs used in the file test\_gpio.c example.

| Function declaration                    | Description                                                                                                                                                                                                                                                   |

|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| gpio_request (ngpio, label)             | <ul> <li>Requests GPIO.</li> <li>ngpio - The GPIO number, such as 25, that is for GPIO25.</li> <li>label - the name of GPIOI request.</li> <li>Returns 0 if OK, -1 on error.</li> </ul>                                                                       |

| gpio_direction_output (ngpio,<br>value) | <ul> <li>Configures the direction of GPIO to OUT and writes the value to it.</li> <li>ngpio - The GPIO number, such as 25,that is, for GPIO25.</li> <li>value - the value written to this GPIO.</li> <li>Returns 0 if low, 1 if high, -1 on error.</li> </ul> |

| gpio_direction_input (ngpio);           | Configures the direction of GPIO to IN.<br>ngpio - The GPIO number, such as 24, that is for GPIO24;<br>Returns 0 if ok, -1 on error.                                                                                                                          |

| gpio_get_value (ngpio)                  | <ul> <li>Reads the value.</li> <li>ngpio - The GPIO number, such as 24, that is for GPIO24;</li> <li>value - the value written to this GPIO.</li> <li>Returns 0 if low, 1 if high, -1 on error.</li> </ul>                                                    |

Table 4. GPIO APIs and their description

Table continues on the next page...

| Function declaration | Description                                                |

|----------------------|------------------------------------------------------------|

| gpio_free (ngpio)    | Frees the GPIO just requested.                             |

|                      | • ngpio - The GPIO number, such as 24, that is for GPIO24; |

|                      | Returns 0 if ok, -1 on error.                              |

Table 4. GPIO APIs and their description (continued)

### 4.2.4 I2C file

The file uboot/app/test\_i2c.c can be used as an example to test the I2C feature and shows how to write an I2C application.

On Is1021aiot board, first, you need to first include the I2C header file, i2c.h, which includes all interfaces for I2C. Then, you need to read a fixed data from offset 0 of Audio codec device (0x2A), if the data is 0xa0, the message [ok]I2C test ok is displayed on the console.

On Is1043ardb board, read a fixed data from offset 0 of INA220 device(0x40). If the data is 0x39, a message, [ok] I2C test ok is displayed on the console.

The table below shows the APIs used in the sample file, test\_i2c.c.

| Function declaration                                                                   | Description                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| int i2c_set_bus_num (unsigned int bus)                                                 | Sets the I2C bus.<br><sup>bus-</sup> bus index, zero based<br>Returns 0 if OK, -1 on error.                                                                                                                                                                                                                                                                                                                                             |

| int i2c_read (uint8_t chip, unsigned int addr,<br>int alen, uint8_t *buffer, int len)  | <ul> <li>Read data from I2C device chip.</li> <li>chip - I2C chip address, range 0127</li> <li>addr - Memory (register) address within the chip</li> <li>alen - Number of bytes to use for addr (typically 1, 2 for larger memories, 0 for register type devices with only one register)</li> <li>buffer - Where to read/write the data</li> <li>len - How many bytes to read/write</li> <li>Returns 0 if ok, not 0 on error</li> </ul> |

| int i2c_write (uint8_t chip, unsigned int addr,<br>int alen, uint8_t *buffer, int len) | <ul> <li>Writes data to i2c device chip.</li> <li>chip - I2C chip address, range 0127</li> <li>addr - Memory (register) address within the chip</li> <li>alen - Number of bytes to use for addr (typically 1, 2 for larger memories, 0 for register type devices with only one register)</li> <li>buffer - Where to read/write the data</li> <li>len - How many bytes to read/write</li> <li>Returns 0 if ok, not 0 on error</li> </ul> |

Table 5. I2C APIs and their description

### 4.2.5 IRQ file

The file, *uboot/app/test\_irq\_init.c* is an example to test the IRQ and IPI (Inter-Processor Interrupts) feature, and shows how to write an IRQ application.

First, you need the IRQ's header asm/interrupt-gic.h, which includes all interfaces for IRQ. Then, register an IRQ function for SGI 0. After setting a SGI signal, the CPU gets this IRQ and runs the IRQ function. You also need to register a hardware interrupt function to show how to use the external hardware interrupt.

SGI IRQ is used for inter-processor interrupts, and it can only be used between bare metal cores. In case you want to communicate between baremetal core and Linux core, refer to the ICC chapter. SGI IRQ id is 0-15, but 8 is reserved to be used for ICC.

The table below shows the APIs used in the sample file, *test\_irq\_init.c*.

| Return type API name<br>(parameter list)                        | Description                                                                                                                                   |

|-----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| void gic_irq_register (int<br>irq_num, void (*irq_handle)(int)) | Registers an IRQ function.<br>• irq_num- IRQ id, 0-15 for SGI, 16-31 for PPI, 32-1019 for SPI<br>• irq_handle - IRQ function                  |

| void gic_set_sgi (int core_mask,<br>u32 hw_irq)                 | Sets a SGI IRQ signal.<br>• core_mask - target core mas<br>• hw_irq - IRQ id                                                                  |

| void gic_set_target (u32<br>core_mask, unsigned long<br>hw_irq) | Sets the target core for hw IRQ.<br>• core_mask - target core mas<br>• hw_irq - IRQ id                                                        |

| void gic_set_type (unsigned<br>long hw_irq)                     | Sets the type for hardware IRQ to identify whether the corresponding interrupt is edge-<br>triggered or level-sensitive.<br>• hw_irq - IRQ id |

Table 6. IRQ APIs and their description

#### 4.2.6 QSPI file

The file uboot/app/test\_qspi.c provides an example that can be used to test the QSPI feature. The below steps show how to write a QSPI application:

- 1. First, locate the QSPI header files spi\_flash.h and spi.h, which include all interfaces for QSPI.

- 2. Then, initialize the QSPI flash. You need to erase the corresponding flash area and confirm erase operation is successful.

- 3. Now, read or write to the flash with an offset of 0x3f00000 and size of 0x40000.

The table below shows the APIs used in the file  ${\tt test\_qsip.c}$  example.

| spi_find_bus_and_cs(bus,cs, &bus_dev, &new)       Finds if the SPI device already exists.         * "bus" - bus index, zero based.       "bus" - bus index, zero based.         * "cs" - the value to chip select model       "bus_dev" - If the bus is found.         * "new" - If the device is found.       "finds if ok, -ENODEV on error.         spi_flash_probe_bus_cs(bus, cs, speed, mode, &new)       Initializes the SPI flash device.         * "bus" - bus index, zero based.       "cs" - the value to Chip Select model         * "cs" - the value to Chip Select model       "cs" - the value to Chip Select model         * "speed" - SPI flash speed, can use 0       "mode" -SPI flash mode, can use 0         * "new" - If the device is initialized.       Returns 0 if ok, -ENODEV on error. | le.<br>9 0 or CONFIG_SF_DEFAULT_SPEED.   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|

| <ul> <li>bus - bus index, zero based.</li> <li>"cs" – the value to chip select mode.</li> <li>"bus_dev" - If the bus is found.</li> <li>"new" – If the device is found.</li> <li>Returns o if ok, -ENODEV on error.</li> </ul> spi_flash_probe_bus_cs(bus, cs, speed, mode, &new) Initializes the SPI flash device. <ul> <li>"bus" - bus index, zero based.</li> <li>"cs" – the value to Chip Select mode.</li> <li>"speed" – SPI flash speed, can use 0</li> <li>"mode" –SPI flash mode, can use 0</li> <li>"new" – If the device is initialized.</li> </ul>                                                                                                                                                                                                                                                      | le.<br>9 0 or CONFIG_SF_DEFAULT_SPEED.   |

| <ul> <li>"bus_dev" - If the bus is found.</li> <li>"new" – If the device is found.</li> <li>Returns o if ok, -ENODEV on error.</li> <li>spi_flash_probe_bus_cs(bus, cs, speed, mode, &amp;new)</li> <li>Initializes the SPI flash device.</li> <li>"bus" - bus index, zero based.</li> <li>"cs" – the value to Chip Select mod</li> <li>"speed" – SPI flash speed, can use</li> <li>"mode" –SPI flash mode, can use 0</li> <li>"new" – If the device is initialized.</li> </ul>                                                                                                                                                                                                                                                                                                                                    | le.<br>9 0 or CONFIG_SF_DEFAULT_SPEED.   |

| <ul> <li>"new" – If the device is found.</li> <li>Returns o if ok, -ENODEV on error.</li> <li>spi_flash_probe_bus_cs(bus, cs, speed, mode, &amp;new)</li> <li>Initializes the SPI flash device.</li> <li>"bus" - bus index, zero based.</li> <li>"cs" – the value to Chip Select mod</li> <li>"speed" – SPI flash speed, can use</li> <li>"mode" –SPI flash mode, can use 0</li> <li>"new" – If the device is initialized.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                              | 0 or CONFIG_SF_DEFAULT_SPEED.            |

| Returns o if ok, -ENODEV on error.         spi_flash_probe_bus_cs(bus, cs, speed, mode, &new)         Initializes the SPI flash device.         • "bus" - bus index, zero based.         • "cs" - the value to Chip Select mod         • "speed" - SPI flash speed, can use         • "new" - If the device is initialized.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0 or CONFIG_SF_DEFAULT_SPEED.            |

| <ul> <li>spi_flash_probe_bus_cs(bus, cs, speed, mode, &amp;new)</li> <li>Initializes the SPI flash device.</li> <li>"bus" - bus index, zero based.</li> <li>"cs" - the value to Chip Select mod</li> <li>"speed" - SPI flash speed, can use</li> <li>"mode" -SPI flash mode, can use 0</li> <li>"new" - If the device is initialized.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0 or CONFIG_SF_DEFAULT_SPEED.            |

| <ul> <li>mode, &amp;new)</li> <li>"bus" - bus index, zero based.</li> <li>"cs" – the value to Chip Select mod</li> <li>"speed" – SPI flash speed, can use</li> <li>"mode" –SPI flash mode, can use 0</li> <li>"new" – If the device is initialized.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0 or CONFIG_SF_DEFAULT_SPEED.            |

| <ul> <li>"bus" - bus index, zero based.</li> <li>"cs" – the value to Chip Select mod</li> <li>"speed" – SPI flash speed, can use</li> <li>"mode" –SPI flash mode, can use 0</li> <li>"new" – If the device is initialized.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0 or CONFIG_SF_DEFAULT_SPEED.            |

| <ul> <li>"speed" – SPI flash speed, can use</li> <li>"mode" –SPI flash mode, can use 0</li> <li>"new" – If the device is initialized.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0 or CONFIG_SF_DEFAULT_SPEED.            |

| <ul> <li>"mode" –SPI flash mode, can use 0</li> <li>"new" – If the device is initialized.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                          |

| "new" – If the device is initialized.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ) or CONFIG_SF_DEFAULT_MODE.             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                          |

| Returns 0 if ok, - ENODEV on error.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                          |

| dev_get_uclass_priv(new) Gets the SPI flash.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                          |

| "new" - The device being initialized.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                          |

| Returns flash if ok , NULL on error.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                          |

| spi_flash_erase(flash, offset, size) Erases the specified location and length of all.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | of the flash content, erases the content |

| <ul> <li>"flash" - Flash is being initialized.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                          |

| <ul> <li>"offset" – Flash offset address.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                          |

| "size" - Erase the length of the data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | l.                                       |

| Returns 0 if ok, 10 on error.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                          |

| spi_flash_read(flash, offset, len, vbuf) Reads flash data to memory.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                          |

| "flash" - The flash being initialized.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                          |

| <ul> <li>"offset" – Flash offset address.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                          |

| "size" - Read the length of the data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                          |

| Returns 0 if ok, !0 on error.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                          |

| spi_flash_write(flash, offset, len, buf) Writes memory data to flash.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                          |

| "flash" - The flash being initialized.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                          |

| <ul> <li>"offset" – Flash offset address.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                          |

| "size" - Write the length of the data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                          |

| Returns o if ok, 10 on error.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                          |

#### Table 7. QSPI APIs

### 4.2.7 Ethernet

The file uboot/app/test\_net.c provides an example to test the Ethernet feature and shows how to write a net application for using this feature.

Here is an example for the LS1043ARDB (or LS1046ARDB) board.

- 1. Connect one of Ethernet port of LS1043ARDB board to one host machine using Ethernet cable.

- 2. Configure the IP address of the host machine as 192.168.1.2.

- 3. Power up the LS1043ARDB board. If the network is connected, the mesage host 192.168.1.2 is alive is displayed on the console.

- 4. The IP address of the board and host machine are defined in the file test\_net.c. In this file, modify the IP address of LS1043ARDB board using variable <code>ipaddr</code> and change the IP address of host machine using variable <code>ping\_ip</code>.

The table below lists the Net APIs and their description.

| API name (type)                            | Description                                                                                                                                |

|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| void net_init (void)                       | Initializes the network                                                                                                                    |

| int net_loop (enum proto_t protocol)       | Main network processing loop. <ul> <li>enum proto_t protocol - protocol type</li> </ul>                                                    |

| int eth_receive (void *packet, int length) | Read data from NIC device chip. <ul> <li>void *packet</li> <li>length - Network packet length</li> </ul> Returns length                    |

| int eth_send (void *packet, int length)    | Writes data to NIC device chip. <ul> <li>packet - Network packet length</li> <li>length - Network packet length</li> </ul> Returns length. |

#### 4.2.8 USB file

The file <code>uboot/app/test\_usb.c</code> provides an example that can be used to test the USB features. The steps below show how to write a USB application:

- 1. Connect a USB disk to the USB port.

- 2. Include the header file, usb.h, which includes all APIs for USB.

- 3. Initialize the USB device using the usb\_init API.

- 4. Scan the USB storage device on the USB bus using the usb\_stor\_scanAPI.

- 5. Get the device number using the blk\_get\_devnum\_by\_type API.

- 6. Read data from the USB disk using the blk\_dread API.

- 7. Write data to the USB disk using the blk\_dwrite API.

The table below shows the APIs used in the file test usb.c example:

| API name (type)                                                                  | Description                                                                  |

|----------------------------------------------------------------------------------|------------------------------------------------------------------------------|

| int usb_init(void)                                                               | Initializes the USB controller.                                              |

| int usb_stop(void)                                                               | Stops the USB controller.                                                    |

| int usb_stor_scan(int mode)                                                      | Scans the USB and reports device information to the user if mode = 1         |

|                                                                                  | <ul> <li>Mode – if mode = 1, the information is returned to user.</li> </ul> |

|                                                                                  | Returns the current device or -1.                                            |

| struct blk_desc                                                                  | Get a block device by type and number.                                       |

| *blk_get_devnum_by_type(enum if_type<br>if_type, int devnum)                     | <ul> <li>If_type – Block device type</li> </ul>                              |

|                                                                                  | devnum - device number                                                       |

|                                                                                  | Returns point to block device descriptor, or NULL if not found.              |

| unsigned long blk_dread(struct blk_desc                                          | Reads data from USB device                                                   |

| *block_dev, lbaint_t start, lbaint_t blkcnt,<br>void *buffer);                   | <ul> <li>block_dev – block device descripter</li> </ul>                      |

|                                                                                  | start – start block                                                          |

|                                                                                  | <ul> <li>blkcnt – block number</li> </ul>                                    |

|                                                                                  | <ul> <li>buffer – buffer to store the data</li> </ul>                        |

|                                                                                  | Returns the block number from which, data is read.                           |

| unsigned long blk_dwrite(struct blk_desc                                         | Writes data to USB device                                                    |

| <pre>*block_dev, lbaint_t start, lbaint_t blkcnt,<br/>const void *buffer);</pre> | <ul> <li>block_dev – block device descripter</li> </ul>                      |

|                                                                                  | start – start block                                                          |

|                                                                                  | blkcnt – block number                                                        |

|                                                                                  | <ul> <li>buffer – buffer to store the data</li> </ul>                        |

|                                                                                  | Returns the block number to which data is written.                           |

#### Table 9. USB APIs and their description

### 4.2.9 PCle file

The file  $app/test_pcie.c$  provides a sample code to test PCIe and network card (such as e1000) features. The steps below show how to write a PCIe and net application:

- 1. Insert a PCIe network card (such as e1000) into PCIe2, or PCIe3 slot (if it exists).

- 2. Configure the IP address of the host machine to 192.168.1.2.

- 3. Include the files include/pci.h and include/ netdev.h.

- 4. Initialize the PCIe controller using the pci\_init API.

- 5. Get uclass device by its name using the uclass\_get\_device\_by\_seq API.

- 6. Initialize the PCIe network device using the pci\_eth\_init API.

- 7. Begin pinging the host machine using the net\_loop API.

The table below shows the APIs used in the file test\_pcie.c example.

| API name (type)                                                                    | Description                                                                   |

|------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|

| void pci_init(void)                                                                | Initializes the PCIe controller. Does not return a value.                     |

| int uclass_get_device_by_seq(enum<br>uclass_id id, int seq, struct udevice **devp) | Gets the uclass device based on an ID and sequence:                           |

|                                                                                    | <ul> <li>id – uclass ID</li> </ul>                                            |

|                                                                                    | seq – sequence                                                                |

|                                                                                    | devp – Pointer to device                                                      |

|                                                                                    | Returns 0 if Ok, negative on error.                                           |

| static inline int pci_eth_init(bd_t *bis)                                          | Initializes network card on the PCIe bus                                      |

|                                                                                    | <ul> <li>Bis – struct containing variables accessed by shared code</li> </ul> |

|                                                                                    | Returns the number of network cards.                                          |

| int net_loop (enum proto_t protocol)                                               | Main network processing loop.                                                 |

|                                                                                    | enum proto_t protocol - protocol type                                         |

|                                                                                    | Returns 0 if Ok, negative value on error.                                     |

#### Table 10. PCIe APIs and their description

#### 4.2.10 CAN file

The file  $app/test_flexcan.c$  provides a sample test case to test flexcan and CANopen features. The following steps show the design process:

- 1. Register the receive interruption function for flexcan.

- 2. Register an overflow interruption function for flextimer.

- 3. Initialize a list of callback functions.

- 4. Set the node ID of this node.

The table below shows the APIs used in the file test\_flexcan.c example.

| API name (type)                                                        | Description                                                                                                                |

|------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| void test_flexcan(void)                                                | It is the test code entry for flexcan.                                                                                     |

| void flexcan_rx_irq(struct can_module<br>*canx)                        | Flexcan receive interruption function. <ul> <li>canx – flexcan interface</li> </ul>                                        |

| void flexcan_receive(struct can_module<br>*canx, struct can_frame *cf) | Flexcan receives CAN data frame.<br>• canx – flexcan interface<br>• cf – CAN message                                       |

| UNS8 setState(CO_Data* d,<br>e_nodeState newState)                     | Sets node state<br>• d – object dictionary<br>• newState – The state that needs to be set<br>Returns 0 if Ok, > 0 on error |

Table 11. CAN APIs and their description

Table continues on the next page...

| void canDispatch(CO_Data* d, Message<br>*m)                        | <ul> <li>CANopen handles data frames that CAN receive:</li> <li>d – object dictionary</li> <li>m – Received CAN message</li> </ul> |

|--------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| int flexcan_send(struct can_module<br>*canx, struct can_frame *cf) | flexcan interface sends CAN message<br>• canx – flexcan interface<br>• cf – CAN message                                            |

| void flextimer_overflow_irq(void)                                  | Flextimer overflow interruption handler function                                                                                   |

| void timerForCan(void)                                             | CANopen virtual clock. Call this function per 100us.                                                                               |

#### Table 11. CAN APIs and their description (continued)

• The following log shows the CANopen slave node state:

=> flexcan error: 0x42242! Note: slave node entry into the stop mode! Note: slave node initialization is complete! Note: slave node entry into the preOperation mode! Note: slave node entry into the operation mode! Note: slave node initialization is complete! Note: slave node entry into the preOperation mode! Note: slave node entry into the operation mode!

#### 4.2.11 ENETC file

The file app/test\_net.c provides an example to test ENETC Ethernet feature and shows how to write a net application for using this feature. This is a special case of using Net APIs.

test\_net for ENETC is only an example for the LS1028ARDB board (CONFIG\_ENETC\_COREID\_SET enabled).

- 1. Connect ENETC port of LS1028ARDB board to one host machine using Ethernet cable.

- 2. Configure the IP address of the host machine as 192.168.1.2.

- 3. Power up the LS1028ARDB board. If the network is connected, the mesage host 192.168.1.2 is alive is displayed on the console.

- 4. The IP address of the board and host machine are defined in the file test\_net.c. In this file, modify the IP address of LS1028ARDB board using variable <code>ipaddr</code> and change the IP address of host machine using variable <code>ping\_ip</code>.

The table below lists the Net APIs for ENETC and their description, refer to section 4.2.7 for other Net APIs.

| API name (type)           | Description                                               |

|---------------------------|-----------------------------------------------------------|

| void pci_init(void)       | Initializes the PCIe controller. Does not return a value. |

| void eth_initialize(void) | Initializes the ethernet.                                 |

### 4.3 ICC module

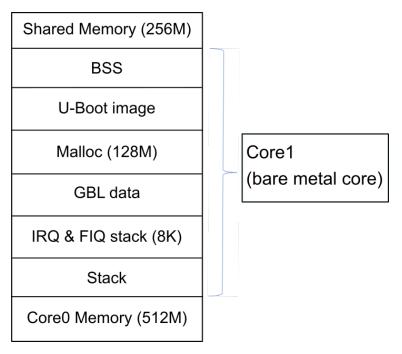

Inter-core communication (ICC) module works on Linux core (master) and Baremetal core (slave), provides the data transfer between cores via SGI inter-core interrupt and share memory blocks. It can support multi-core silicon platform and transfer the data concurrently and efficiently.

ICC module is structured based on two basics:

- SGI: Software-generated Interrupts in ARM GIC, used to generate inter-core interrupts. The ICC module uses the number 8 SGI interrupt for all Linux and Baremetal cores.

- Shared memory: A memory space shared by all platform cores. The base address and size of the share memory should be defined in header files before compilation.

ICC modules can work concurrently, lock-free among multi-core platform, and support broadcast case with Buffer Descriptor Ring mechanism.

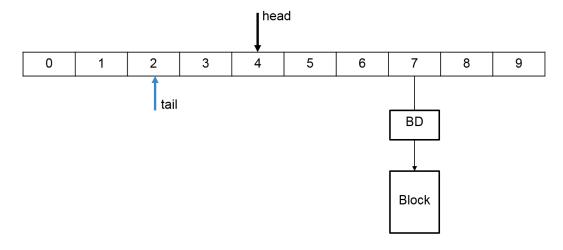

The figure below shows the basic operating principle for data transfer from Core 0 to Core 1. After the data writing and head point moving to next, Core 0 triggers a SGI (8) to Core 1, then Core 1 gets the BD ring updated status and reads the new data, then moves the tail point to next.

Figure 6. BD rings for inter-core communication

For a multi-core platform (that is, four cores), the total BD rings are arranged as shown in the following figure. (See the BD rings on Core 0 and Core 1.)

| Core0 to Core1 | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 |

|----------------|---|---|---|---|---|---|---|---|---|---|

| Core0 to Core2 | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 |

| Core0 to Core3 | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 |

|                |   |   |   |   |   |   |   |   |   |   |

| Core1 to Core0 | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 |

| Core1 to Core2 | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 |

| Core1 to Core3 | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 |

#### Figure 7. BD rings for multi-core platform

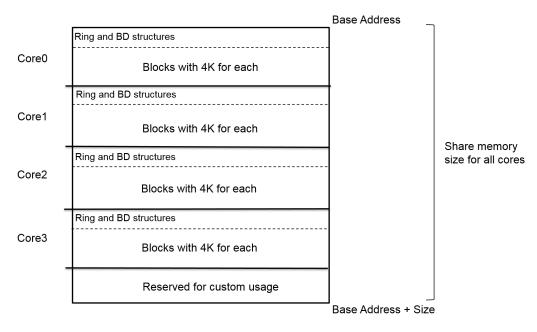

All the ICC ring structures, BD structures and blocks for data are in the shared memory. A four-core platform ICC module would map the shared memory as shown in the figure below.

Figure 8. ICC shared memory map for the four-core platform

Generally, Core 0 runs Linux as master core, other cores run Baremetal as slaves. They obtain the same size of share memory to structure the rings and BDs, and split the blocks space with 4k unit for each block. The reserved space at the top of the share memory is out of the ICC module and for the custom usage.

For LS1021A platform with two cores, the share memory map is defined as:

- The total share memory size is 256 MB.

- The reserved space for custom usage is 16 MB at the top of the share memory space.

- Core 0 runs Linux as master core, the share memory size for ICC is 120 MB, in which the ring and BD structure space is 2 M, and the block space for data is 118 MB with 4K for each block.

- Core 1 runs Baremetal as slave core, the share memory size for ICC is 120 MB, in which the ring and BD structure space is 2M, and the block space for data is 118 MB with 4K for each block.

The ICC module includes two parts of the code:

- ICC code for Linux user space, works for data transfer between master core and slave cores. The code is integrated into the OpenIL and named icc package. After the compilation, the icc binary is put into the Linux filesystem.

- ICC code for Baremetal, runs on every slave core, works for data transfer between baremetal cores and master core.

The ICC code for Linux user space in OpenIL directory:

package/icc/src/

- ---- icc-main.c --- the example case commands

- ----- inter-core-comm.c

- inter-core-comm.h --- include the header file to use ICC module

- L- Makefile

The ICC code for Baremetal in Baremetal directory:

baremetal/

----- arch/arm/lib/inter-core-comm.c

---- arch/arm/include/asm/inter-core-comm.h --- include the header file to use ICC module

L--- cmd/icc.c --- the example case commands

The APIs ICC exported out for usage in both Linux user space and Baremetal code.

| APIs                                                                                             | Description                                                                                                           |  |

|--------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|--|

| unsigned long icc_ring_state(int coreid)                                                         | Checks the ring and block state.<br>Returns:<br>• 0 - if empty<br>• !0 - the working block address currently.         |  |